22530007

## 人工智能与芯片设计

3-单核CPU

燕博南 2023秋

### **Instruction Set Architecture (ISA)**

- The contract between software and hardware

- Typically described by giving all the programmer-visible state (registers + memory)

plus the semantics of the instructions that operate on that state

- IBM 360 was first line of machines to separate ISA from implementation (aka. *microarchitecture*)

- Many implementations possible for a given ISA

- E.g., Soviets built code-compatible clones of the IBM360, as did Amdahl after he left IBM

- E.g.2., AMD, Intel, VIA processors run the AMD64 ISA

- E.g.3: many cellphones use the ARM ISA with implementations from many different companies including Apple, Qualcomm, Samsung, Huawei, etc.

- We use ARM/RISC-V as standard ISA in class (www.riscv.org)

- Many companies and open-source projects build RISC-V implementations

### ISA to Microarchitecture Mapping

- ISA often designed with particular microarchitectural style in mind,

- e.g.,

Accumulator/Adder  $\Rightarrow$  hardwired, unpipelined CISC (Complex instruction set computer)  $\Rightarrow$  microcoded RISC (Reduced instruction set computer)  $\Rightarrow$  microcoded, pipelined VLIW (Very long instruction word)  $\Rightarrow$  fixed-latency in-order parallel pipelines JVM (Java virtual machine)  $\Rightarrow$  software interpretation

- But can be implemented with any microarchitectural style

- Intel Ivy Bridge: hardwired pipelined CISC (x86) machine (with some microcode support)

- Apple M1/M2 (native ARM ISA, emulates x86 in software)

- ARM Jazelle: A hardware JVM processor

- This lecture: a microcoded RISC-V machine

#### **Control versus Datapath**

- Processor designs can be split between

- *datapath*, where numbers are stored and arithmetic operations computed, and

- *control*, which sequences operations on datapath

# A computer is just a big fancy state machine.

### John von Neumann

- In the old days, "programming" involved actually changing a machine's physical configuration by flipping switches or connecting wires.

- A computer could run just one program at a time.

- Memory only stored data that was being operated on.

- Then around 1944, John von Neumann and others got the idea to encode instructions in a format that could be stored in memory just like data.

- The processor interprets and executes instructions from memory.

- One machine could perform many different tasks, just by loading different programs into memory.

- The "stored program" design is often called a Von Neumann machine.

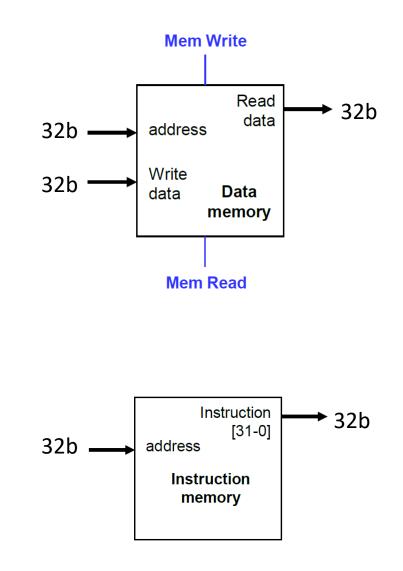

#### Memories

- Harvard architecture :

- programs and data stored in separate memories.

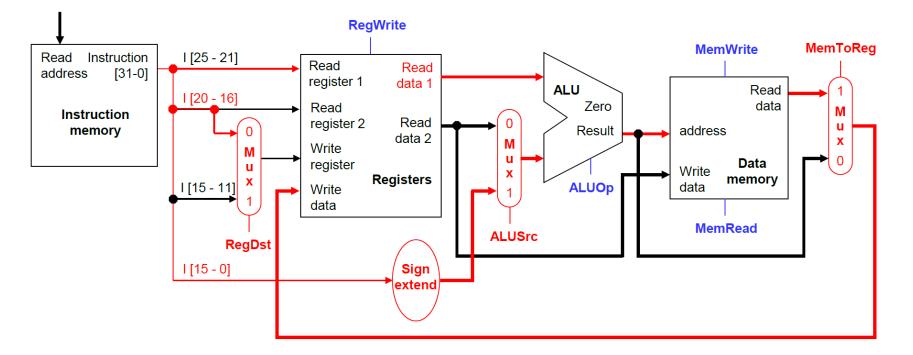

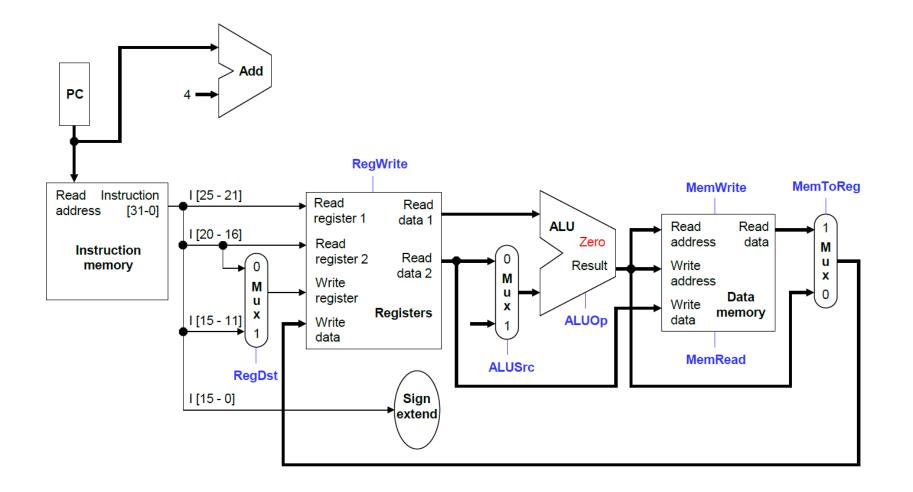

- Blue lines represent control signals. MemRead and MemWrite should be set to 1 if the data memory is to be read or written respectively, and 0 otherwise.

- When a control signal does something when it is set to 1, we call it active high(vs. active low) because 1 is usually a higher voltage than 0.

- Pretend it's already loaded with a program, which doesn't change while it's running.

### **Instruction Fetching**

- The CPU is in a infinite loop

- The program counter or PC register holds the address of the current instruction

- Given our instruction is 4 byte (32b) long

- >> PC = PC + 4 after obtaining an instruction

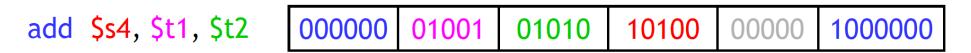

### **Encoding R-type instructions**

- Register-to-register arithmetic instructions use the R-type format.

- op is the instruction opcode, and func specifies a particular arithmetic operation

- rs, rt and rd are source and destination registers.

| ор     | rs     | rt     | rd     | shamt  | func   |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

• Example

Now pretend you know assembly!

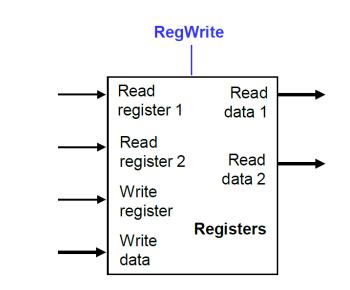

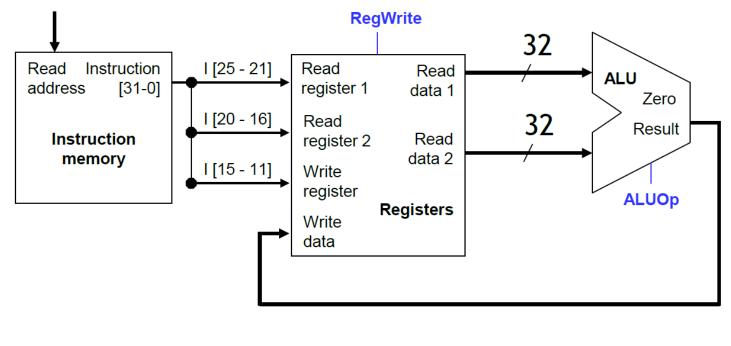

### **Register File & ALU**

- R-type instructions must access registers and an ALU

- Our register file stores thirty-two 32-bit values.

- Each register specifier is 5 bits long.

- You can read from two registers at a time (2 ports).

- **RegWrite** is 1 if a register should be written.

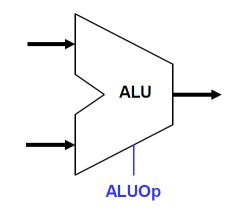

- Here's a simple ALU with five operations, selected by a 3-bit control signal ALUOp.

| ALUOp | Function |

|-------|----------|

| 000   | and      |

| 001   | or       |

| 010   | add      |

| 110   | subtract |

| 111   | slt      |

### **Executing an R-type instruction**

| C  | р  | r  | ГS | r  | t  | r  | d  | sha | mt |   | func |

|----|----|----|----|----|----|----|----|-----|----|---|------|

| 31 | 26 | 25 | 21 | 20 | 16 | 15 | 11 | 10  | 6  | 5 | 0    |

- Fetch an instruction from "instruction memory"

- Fetch data from registers rs & rt

- ALU does computation

- Put results into rd

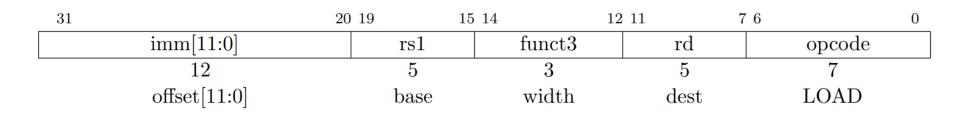

### **Encoding I-type instructions**

- Immediate number instructions (I-type)

- Rt is the destination for lw, but a source for beq and sw

- Address is a 16-bit signed constant

| immediate | rs1    | funct3 | rd     | opcode |

|-----------|--------|--------|--------|--------|

| 12 bits   | 5 bits | 3 bits | 5 bits | 7 bits |

• Example

ld x9, 64(x22) // Temporary reg x9 gets A[8]

### **Accessing Data Memory**

ld x9, 64(x22) // Temporary reg x9 gets A[8]

Data memory Address: (the content in x22)+64 Operation: load the data in the "data memory" into x9

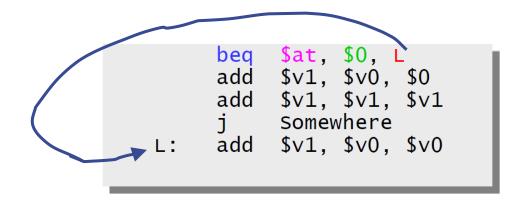

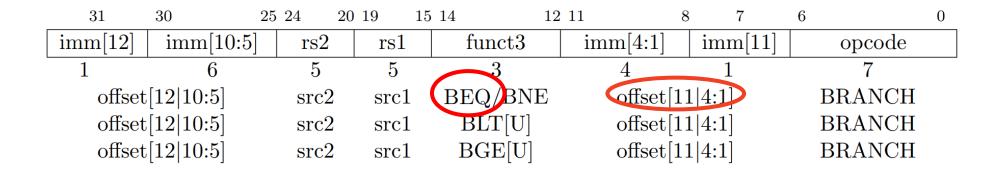

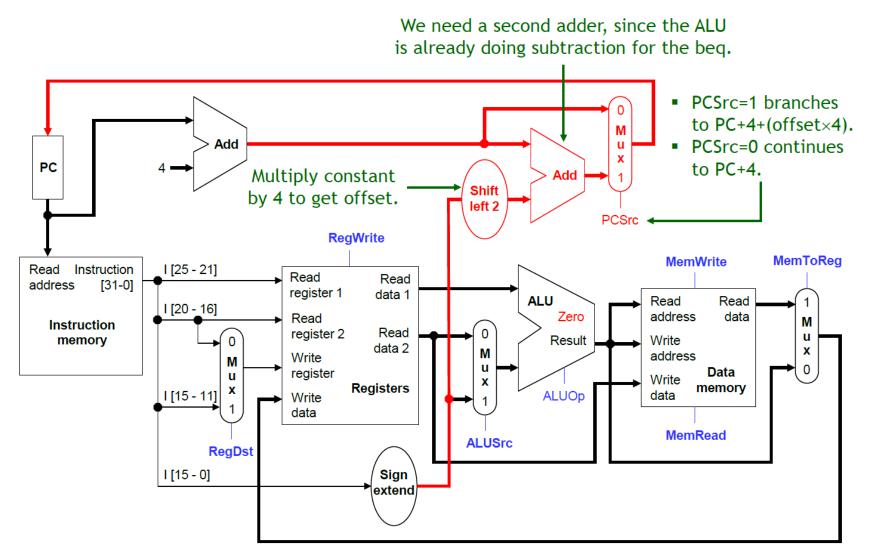

#### Branches

• For branch instructions, next PC should be obtained in the

BEQ: if rs1==rs2, then to go to the current PC+offset

### So Execute BEQ should be:

- 1. Fetch the instruction, like beq \$at, \$0, offset, from memory.

- 2. Compare \$at and \$0

- 3. If yes, next PC = PC + offset \* 4 byte/instruction

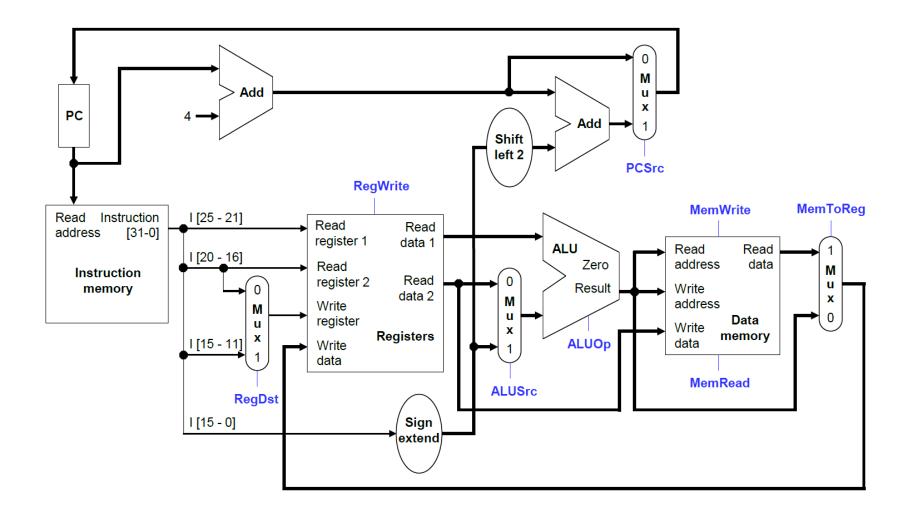

#### Hardware

#### Hardware

#### **Final Hardware**

## Review A Little Bit

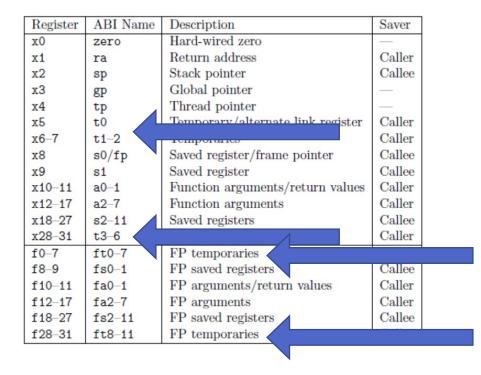

#### **Review: RV32I Processor State**

Program counter (pc)

32x32-bit integer registers (x0-x31)x0 always contains a 0

32 floating-point (FP) registers (f0-f31)

each can contain a single- or double-precision FP value (32-bit or 64-bit IEEE FP)

FP status register (**fcsr**), used for FP rounding mode & exception reporting

| XLEN-1    | 0 |

|-----------|---|

| x0 / zero |   |

| x1        |   |

| x2        |   |

| x3        |   |

| x4        |   |

| x5        |   |

| x6        |   |

| x7        |   |

| x8        |   |

| x9        |   |

| x10       |   |

| x11       |   |

| x12       |   |

| x13       |   |

| x14       |   |

| x15       |   |

| x16       |   |

| x17       |   |

| x18       |   |

| x19       |   |

| x20       |   |

| x21       |   |

| x22       |   |

| x23       |   |

| x24       |   |

| x25       |   |

| x26       |   |

| x27       |   |

| x28       |   |

| x29       |   |

| x30       |   |

| x31       |   |

| XLEN      |   |

| XLEN-1    | 0 |

| pc        |   |

| XLEN      |   |

| FLEN-1 |      | 0 |

|--------|------|---|

|        | fO   |   |

|        | f1   |   |

|        | f2   |   |

|        | f3   |   |

|        | f4   |   |

|        | f5   |   |

|        | f6   |   |

|        | f7   |   |

|        | f8   |   |

|        | f9   |   |

|        | f10  |   |

|        | f11  |   |

|        | f12  |   |

|        | f13  |   |

|        | f14  |   |

|        | f15  |   |

|        | f16  |   |

|        | f17  |   |

|        | f18  |   |

|        | f19  |   |

|        | f20  |   |

|        | f21  |   |

|        | f22  |   |

|        | f23  |   |

|        | f24  |   |

|        | f25  |   |

|        | f26  |   |

|        | f27  |   |

|        | f28  |   |

|        | f29  |   |

|        | f30  |   |

|        | f31  |   |

|        | FLEN |   |

| 31     |      | 0 |

|        | fcsr |   |

|        | 32   |   |

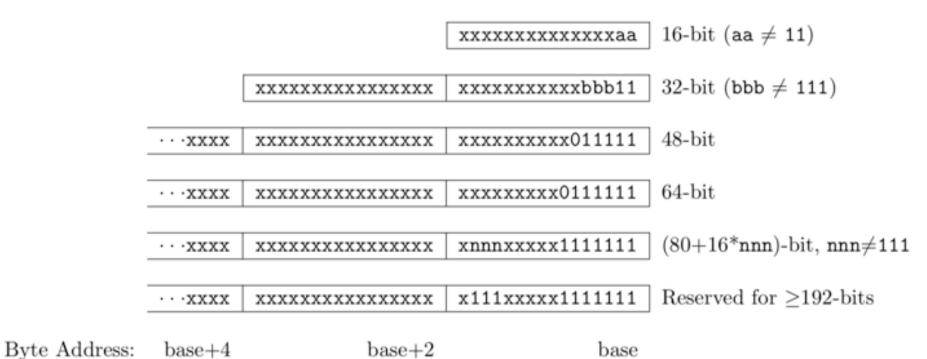

### **RISC-V Instruction Encoding**

- Can support variable-length instructions.

- Base instruction set (RV32) always has fixed 32-bit instructions lowest two bits = 11<sub>2</sub>

- All branches and jumps have targets at 16-bit granularity (even in base ISA where all instructions are fixed 32 bits)

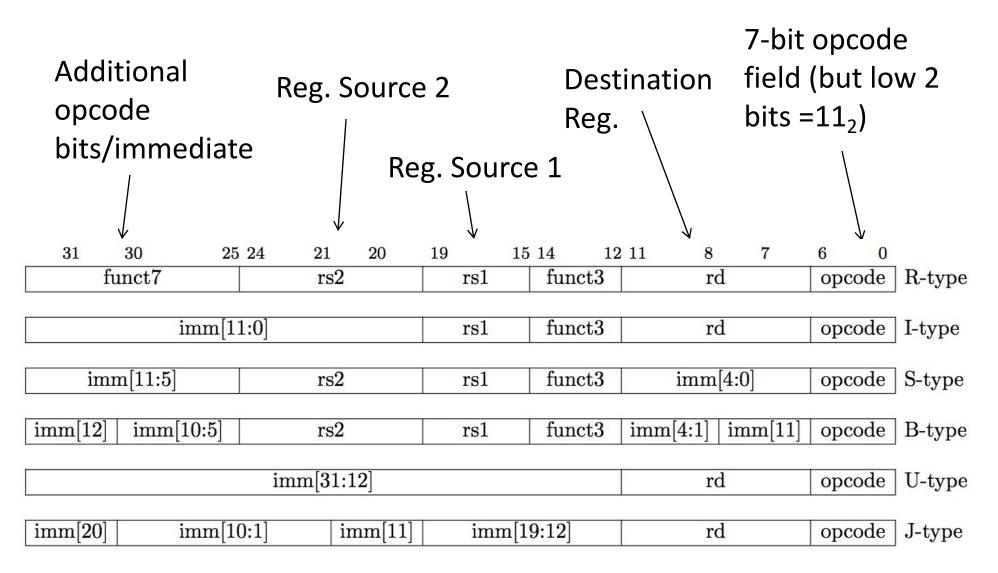

#### **RISC-V Instruction Formats**

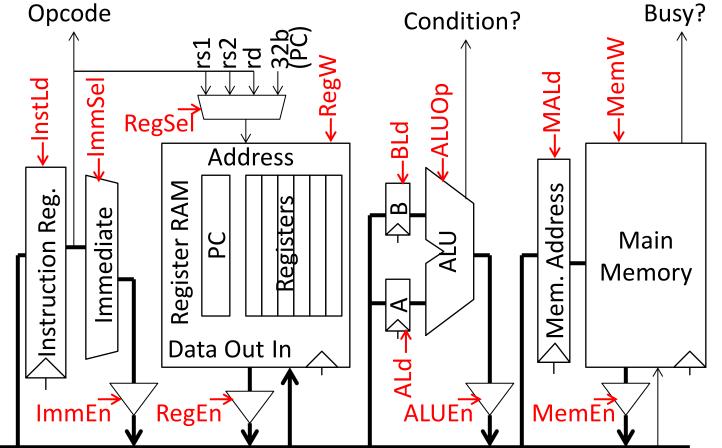

#### **Single-Bus Datapath for Microcoded RISC-V**

Microinstructions written as register transfers:

- MA:=PC means RegSel=PC; RegW=0; RegEn=1; MALd=1

- B:=Reg[rs2] means RegSel=rs2; RegW=0; RegEn=1; BLd=1

- Reg[rd]:=A+B means ALUop=Add; ALUEn=1; RegSel=rd; RegW=1

### **Inside Instruction Memory**

|        | Address |           |      | Data                |          |

|--------|---------|-----------|------|---------------------|----------|

| μΡϹ    | Opcode  | e Cond? B | usy? | Control Lines       | Next µPC |

| fetch0 | Х       | Х         | Х    | MA,A:=PC            | fetch1   |

| fetch1 | Х       | Х         | 1    | 1                   | fetch1   |

| fetch1 | Х       | Х         | 0    | IR:=Mem             | fetch2   |

| fetch2 | ALU     | Х         | Х    | PC:=A+4             | ALU0     |

| fetch2 | ALUI    | Х         | Х    | PC:=A+4             | ALUI0    |

| fetch2 | LW      | Х         | Х    | PC:=A+4             | LWO      |

| ••••   |         |           |      |                     |          |

|        |         |           |      |                     |          |

| ALU0   | Х       | Х         | Х    | A:=Reg[rs1]         | ALU1     |

| ALU1   | Х       | Х         | Х    | B:=Reg[rs2]         | ALU2     |

| ALU2   | Х       | Х         | Х    | Reg[rd]:=ALUOp(A,B) | fetch0   |

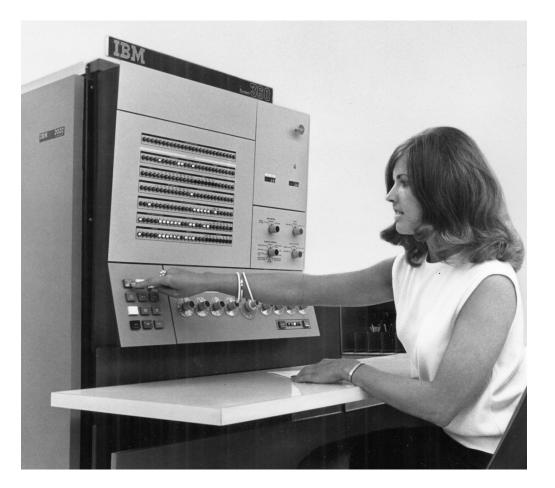

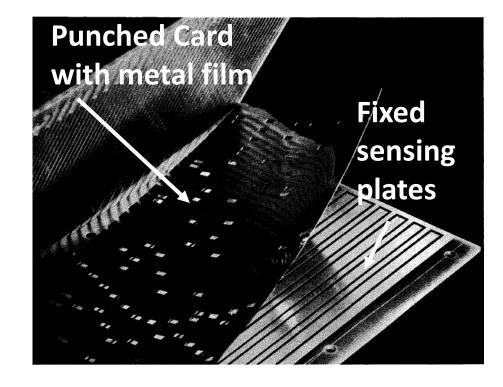

### **Back Into History**

IBM 360

#### IBM 360

#### ISA Compatible Computers

|                        | M30  | M40  | M50  | M65  |

|------------------------|------|------|------|------|

| Datapath width (bits)  | 8    | 16   | 32   | 64   |

| µinst width (bits)     | 50   | 52   | 85   | 87   |

| μcode size (K μinsts)  | 4    | 4    | 2.75 | 2.75 |

| μstore cycle (ns)      | 750  | 625  | 500  | 200  |

| memory cycle (ns)      | 1500 | 2500 | 2000 | 750  |

| Rental fee (\$K/month) | 4    | 7    | 15   | 35   |

• Only the fastest models (75 and 95) were hardwired

## Assembly Language Snap Tutorial

#### **Temporaries**

### **Basic (Integer) Commends**

|        | Instruction<br>Example | Description                                                                                                                                                                   |

|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | lb t0, 8(sp)           | Loads (dereferences) from memory<br>address (sp + 8) into register t0.<br>lb = load byte, lh = load halfword,<br>lw = load word, ld = load<br>doubleword.                     |

|        | sb t0, 8(sp)           | <pre>Stores (dereferences) from register<br/>t0 into memory address (sp + 8). sb<br/>= store byte, sh = store halfword,<br/>sw = store word, sd = store<br/>doubleword.</pre> |

|        | add a0, t0, t1         | Adds value of t0 to the value of t1 and stores the sum into a0.                                                                                                               |

|        | addi a0, t0, -10       | Adds value of t0 to the value -10<br>and stores the sum into a0.                                                                                                              |

|        | sub a0, t0, t1         | Subtracts value of t1 from value of t0 and stores the difference in a0.                                                                                                       |

| ]      | mul a0, t0, t1         | Multiplies the value of t0 to the value of t1 and stores the product in a0.                                                                                                   |

|        | div a1, s3, t3         | Dividies the value of t3<br>(denominator) from the value of s3<br>(numerator) and stores the quotient<br>into the register a1.                                                |

|        | rem a1, s3, t3         | Divides the value of t3<br>(denominator) from the value of s3<br>(numerator) and stores the remainder<br>into the register a1.                                                |

| Peking | University             |                                                                                                                                                                               |

| and a3, t3, s3 | Performs logical AND on operands t3<br>and s3 and stores the result into<br>the register a3. |

|----------------|----------------------------------------------------------------------------------------------|

| or a3, t3, s3  | Performs logical OR on operands t3<br>and s3 and stores the result into<br>the register a3.  |

| xor a3, t3, s3 | Performs logical XOR on operands t3<br>and s3 and stores the result into<br>the register a3. |

sub a0, zero, a1

Translate: a0 = 0 - a1

### **Floating-Point Assembly**

| 1 | # Load a double-precision value                       |

|---|-------------------------------------------------------|

| 2 | flw ft0, 0(sp)                                        |

| 3 | # ft0 now contains whatever we loaded from memory + 0 |

| 4 | flw ft1, 4(sp)                                        |

| 5 | # ft1 now contains whatever we loaded from memory + 4 |

| 6 | fadd.s ft2, ft0, ft1                                  |

| 7 | # ft2 is now ft0 + ft1                                |

#### RISC-V supports floating-point

| In fact, RISC-V has many |  |

|--------------------------|--|

| modules:                 |  |

| Base      | Version    | Status   |  |

|-----------|------------|----------|--|

| RVWMO     | 2.0        | Ratified |  |

| RV32I     | <b>2.1</b> | Ratified |  |

| RV64I     | <b>2.1</b> | Ratified |  |

| RV32E     | 1.9        | Draft    |  |

| RV128I    | 1.7        | Draft    |  |

| Extension | Version    | Status   |  |

| M         | 2.0        | Ratified |  |

|           | <b>2.1</b> | Ratified |  |

| F         | <b>2.2</b> | Ratified |  |

| D         | 2.2        | Ratified |  |

| Q         | <b>2.2</b> | Ratified |  |

| C         | 2.0        | Ratified |  |

| Counters  | 2.0        | Draft    |  |

| L         | 0.0        | Draft    |  |

| B         | 0.0        | Draft    |  |

| J         | 0.0        | Draft    |  |

| T         | 0.0        | Draft    |  |

| P         | 0.2        | Draft    |  |

| V         | 0.7        | Draft    |  |

| Zicsr     | 2.0        | Ratified |  |

| Zifencei  | 2.0        | Ratified |  |

| Zam       | 0.1        | Draft    |  |

| Ztso      | 0.1        | Frozen   |  |

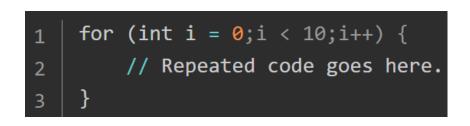

#### Branching

| 1 | # t0 = 0 | )    |      |       |      |

|---|----------|------|------|-------|------|

| 2 | li       | t0,  | 0    |       |      |

| 3 | li       | t2,  | 10   |       |      |

| 4 | loop_hea | d:   |      |       |      |

| 5 | bge      | t0,  | t2,  | loop_ | _end |

| 6 | # Repeat | ed o | ode  | goes  | here |

| 7 | addi     | t0,  | t0,  | 1     |      |

| 8 | j        | loop | _hea | ad    |      |

| 9 | loop_end | :    |      |       |      |

#### **Example: Use the Stack**

sp is a special register that is a stack

Statck: last in first out (LIFO)

| 1 | addi | sp, sp, - <mark>8</mark> |

|---|------|--------------------------|

| 2 | sd   | ra, 0(sp)                |

| 3 | call | printf                   |

| 4 | ld   | ra, 0(sp)                |

| 5 | addi | sp, sp, <mark>8</mark>   |

| 6 | ret  |                          |

#### **C** Function

| 1  | <pre>my_function:</pre> |     |                      |  |  |  |

|----|-------------------------|-----|----------------------|--|--|--|

| 2  | # Prologue              |     |                      |  |  |  |

| 3  | addi                    | sp, | sp, -32              |  |  |  |

| 4  | sd                      | ra, | 0(sp)                |  |  |  |

| 5  | sd                      | a0, | <mark>8(</mark> sp)  |  |  |  |

| 6  | sd                      | s0, | <mark>16(</mark> sp) |  |  |  |

| 7  | sd                      | s1, | 24(sp)               |  |  |  |

| 8  |                         |     |                      |  |  |  |

| 9  | # Epilogue              |     |                      |  |  |  |

| 10 | ld                      | ra, | 0(sp)                |  |  |  |

| 11 | ld                      | a0, | <mark>8(</mark> sp)  |  |  |  |

| 12 | ld                      | s0, | <mark>16(</mark> sp) |  |  |  |

| 13 | ld                      | s1, | 24(sp)               |  |  |  |

| 14 | addi                    | sp, | sp, 32               |  |  |  |

| 15 | ret                     |     |                      |  |  |  |

#### Good News is …

- We have compiler that can convert C code into assembly

- <u>搭建RISC-V编译环境与运行环境 知乎 (zhihu.com)</u>

- <u>riscv-collab/riscv-gnu-toolchain: GNU toolchain for RISC-V</u>, <u>including GCC (github.com)</u>

### Hardware Code Examples

- Counter

- Finite State Machine

- Memory

- <u>https://bonany.gitlab.io/pis/</u>

- Arithmetic Logic Units