# AI ASIC: Design and Practice (ADaP) Fall 2024 HDL Simulators & Logic Synthesis

燕博南

- Verilog HDL Simulators

- Logic Synthesis A instrumentalism Perspective

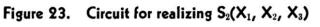

- How to synthesis RTL code to logic gates?

**RTL: Register Transfer Level**

# Part 1

Open-source simulators for HDL

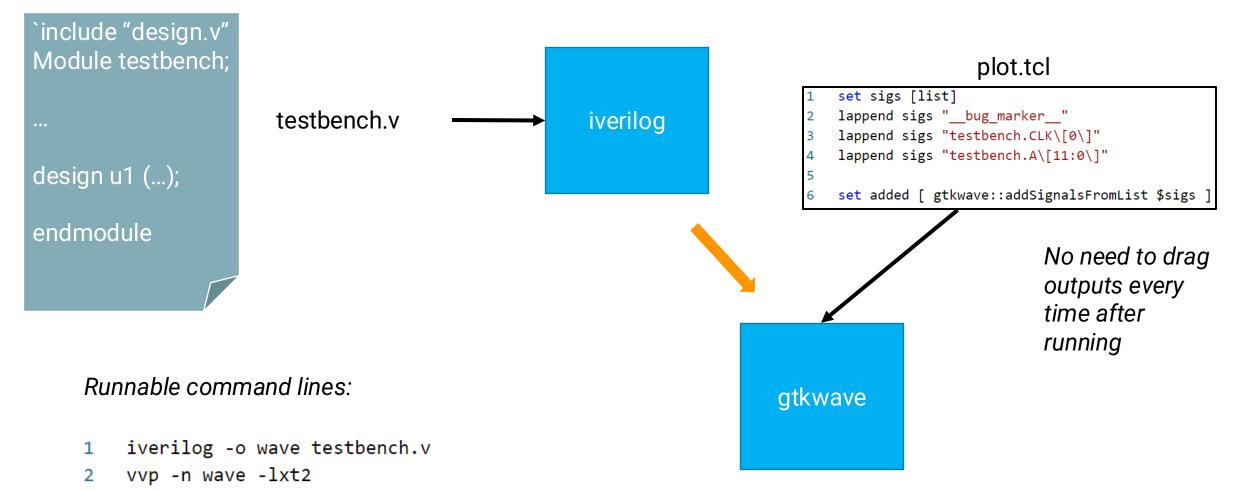

#### Verilog Simulator Workflow

## Verilog Simulator Workflow

3 gtkwave wave.vcd -S plot.tcl

A good tutorial: <u>全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程</u>

#### Other simulators

- Verilator

- PyRTL

- VCS

- Incisive

- Modelsim

• ...

What are their differences?

# Part 2

Logic Synthesis

# Definition: Synthesize logic circuits into gates (gate-level netlist)

- Quick (re)design time

- Separate functionality, technology-dependent parameters, and design constraints

- Fast timing/area/power estimates

Why "synthesis" works? Why can we synthesize logic?

A Symbolic Analysis of Relay and Switching Circuits By CLAUDE E. SHANNON ENROLLED STUDENT AIEE

Figure 24. Simplification of figure 23

#### Outputs of logic synthesis?

PEKING UNIVERSITY

- Timing/Area/Power reports

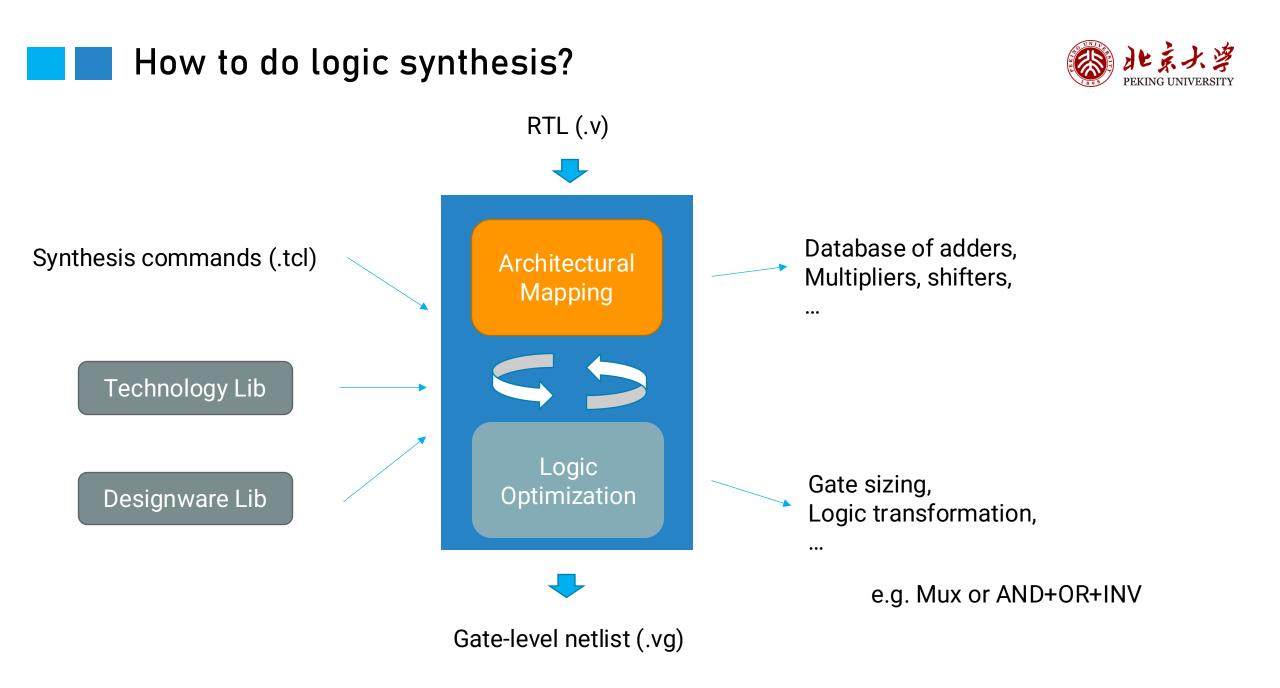

- Gate-level netlist (.vg) & timing info. In standard delay format (.sdf) for timing-aware simulation

- Pre-syn (RTL) sim needs: testbench.v, design.v

- Post-syn sim needs: testbench.v, design.vg, design.sdf, stdlib\_cells.v

#### e.g. Assign C=A+B

# Synthesis Tool: Synopsys Design Compiler

- dc\_shell-t or dc\_shell-xg-t

- Command line approach (no gui)

- Other synthesis tools also work fine:

- Cadence Genus

- Open Road: yosys

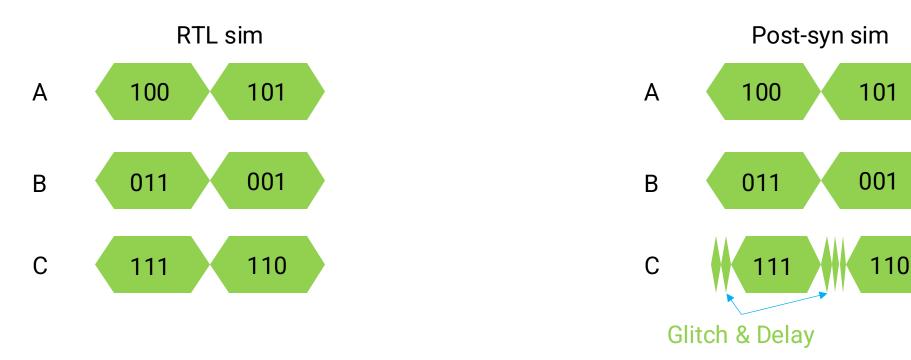

## Script Example (.tcl file)

- 1. RTL coding

- 2. Technology lib setup

- 3. Constraints

- 4. Major synthesis commands

- 5. Gate-level simulation

# 1. RTL coding

- 2. Technology lib setup

- 3. Constraints

- 4. Major synthesis commands

- 5. Gate-level simulation

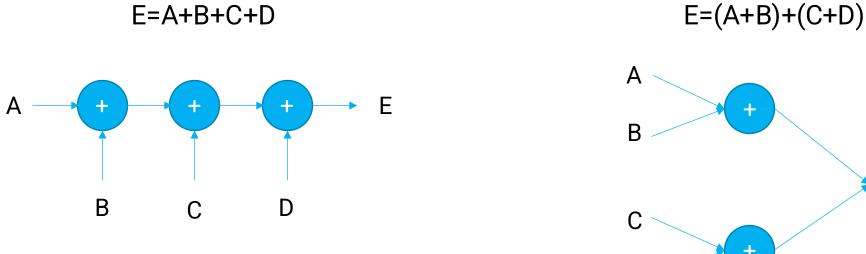

• Different coding styles that are functionally eqvl. may be mapped into HWs having different timing/area

Write Good HDL

Which is better?

- 1. RTL coding

- 2. Technology lib setup

- 3. Constraints

- 4. Major synthesis commands

- 5. Gate-level simulation

#### Technology Lib is about:

- Process

- Operating Condition (ss/tt/ff design corner, temperature, VDD voltage)

- Cell Name

- Area

- Functionality

- Pin Capacitance

- Leakage Power

- Look-up Tables (LUT) for Dynamic Power & Propagation Delay of all i/o Paths

- (idx1: input transition time; idx2: o/p capacitance)

- ...

#### Setup Tech Lib

- set search\_path "\$search\_path \

- 2 /w/apps2/public.2/tech/synopsys/32-28nm/SAED32\_EDK/lib/stdcell\_rvt/db\_nldm"

- 3 set target\_library "saed32rvt\_ff1p16vn40c.db saed32rvt\_ss0p95v125c.db"

- 4 set link\_library "\* saed32rvt\_ff1p16vn40c.db saed32rvt\_ss0p95v125c.db dw\_foundation.sldb"

- 5 set synthetic\_library "dw\_foundation.sldb"

6

- 7 # Define work path (note: The work path must exist, so you need to create a folder WORK first)

- 8 define\_design\_lib WORK -path ./WORK

- 9 set alib\_library\_analysis\_path "./alib-52/"

- DC follows **search\_path** to find libraries you specify

- DC uses cells in target library for logic optimization (so we need to do set\_target\_library first)

- Remember: Use backslash \ before changing lines to avoid compilation errors.

- 1. RTL coding

- 2. Technology lib setup

- 3. Constraints

- 4. Major synthesis commands

- 5. Gate-level simulation

#### Synthesis is Constraint-driven

- You set the goals (through **design constraints**)

- DC optimizes the design to meet your goals

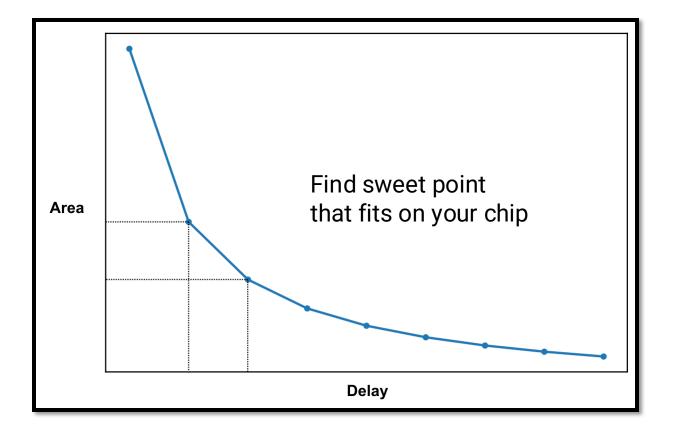

#### Timing Analysis for VLSI

"set\_input\_delay" : affects input logic

"create\_clock": affects internal logic

"set\_output\_delay": affects output logic

**Input delay**: Arrival of an external path w.r.t. the clock edge **Output delay**: timing from an output port of the current design to a register input port of other modules

### **Describe Constraints**

- Clocks

- Period, latency, uncertainty

- Design rules

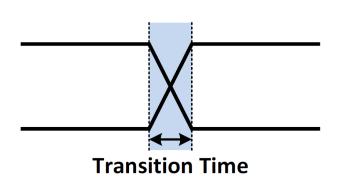

- Maximum transition

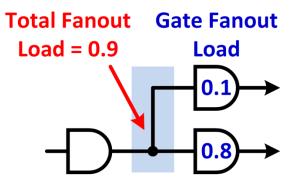

- Maximum capacitance

- Maximum fanout

- Input-related

- Driving cells, Input delay

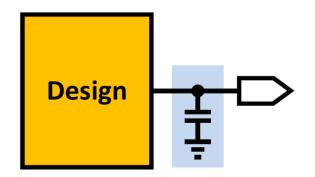

- Output-related

- Load, Output delay

- Exception paths

- False paths, multi-cycle paths

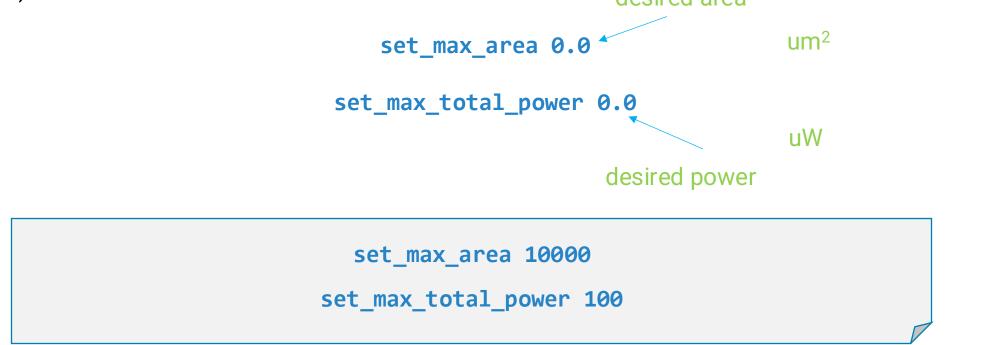

- Optimization goal

- Maximum area/power

**# Accurate constraints** (not too tight/loose): Good integ. results

#### **Clock Description**

• create\_clock: define clock's waveform (e.g. period)

```

create_clock -name "sysclk" -period 2.0 [get_ports "CLK"]

```

• set\_fix\_hold: respect the hold time requirement of all clocked flip-flops

#### set\_fix\_hold sysclk

set\_dont\_touch\_network: do not buffer clock network

set\_dont\_touch\_network [get\_clocks "sysclk"]

• Specify uncertainty (skew + jitter) of clock network

set\_clock\_uncertainty 0.1 [get\_clocks "sysclk"]

• Sets the max\_transition attribute to a specified value on specified clocks group, ports or designs

set\_max\_transition 0.1 current\_design

Constraints: Max transitions, fanout & output loads

• Sets the max\_transition, fanout load & output load attribute :

set\_max\_transition 0.1 current\_design

set\_max\_fanout 1.0 current\_design

set\_load 1.0 [all\_outputs]

#### Constraints: Driving Cells

• Sets attributes on input or inout ports of the current design, specifying that a library cell or output pin of a library cell drives specified ports:

```

set_driving_cell [-library lib] [-lib_cell lib_cell_name] [-pin pin_name]

```

```

set ALL_IN_BUT_CLK [remove_from_collection [all_inputs] "CLK"]

set_driving_cell -no_design_rule -library \

saed32rvt_ss0p95v125c.db:saed32rvt_ss0p95v125c -lib_cell \

DFFASRX2_RVT -pin Q $ALL_IN_BUT_CLK

```

• Removes timing constraints from particular paths, but still needs to satisfy design rule (transition, capacitance, fanout):

```

set_false_path -from [from_list]

```

set\_false\_path -from [get\_ports "TEST\_OUT1"]

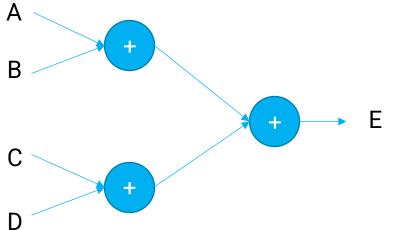

## Constraints: Maximum Area/Power

Optimization goals for your design (DC will do it best to satisfy them, w/o violating the three design rules):

desired area

### **Constraints: Operating Condition**

• Defines the operating conditions for the current design:

set\_operating\_conditions -min ff1p16vn40c -max ss0p95v125c

### **Constraints: Wire-load Models and Modes**

Specify a selection group to use for determining a wire load model to be assigned to designs and cells or to a specified cluster:

```

set_wire_load_selection_group group_name [-max] [-min]

```

set\_wire\_load\_selection\_group group\_name "predcaps"

DC will select proper model based on synthesis area (again, lookup this name in .lib file)

- 1. RTL coding

- 2. Technology lib setup

- 3. Constraints

- 4. Major synthesis commands

- 5. Gate-level simulation

#### **Commands Preview**

- Not all commands introduced are necessarily needed

- Things MUST do

Analyze, elaborate, and link design Compile design

• Things can do based on your needs

Ungroup; Uniquify Clock gating creation Remove unconnected ports

**Suggestion**: Learn by playing w/ different commands and observing the differences

#### Analyze Designs:

• Analyzes the HDL files and stores the intermediate format in the specified library.

analyze [-format vhdl | verilog | sverilog] file\_list

analyze -format Verilog {adder.v}

elaborate

Or

read\_verilog adder.v

• Builds a design from the intermediate format of a Verilog module, a VHDL entity and architecture, or a VHDL configuration:

set design\_name adder

elaborate \$design\_name

or

link

#### **Ungroup & Uniquify**

• Removes a level of hierarchy:

```

ungroup cell_list | -all [-flatten]

```

ungroup -flatten -all

• Removes multiple-instantiated hierarchy in the current design by creating a unique design for each of the cell instances:

uniquify

• Performs logic-level and gate-level synthesis and optimization on the current design:

```

compile [-no_design_rule | -only_design_rule | -only_hold_time] [-

map_effort medium | high] [-boundary_optimization]

```

compile -map\_effort high

compile\_ultra

• Removes unconnected ports or pins from cells, references, and sub-designs

remove\_unconnected\_ports -blast\_buses [get\_cells -hier]

report\_timing -path full -delay min -max\_paths 10 -nworst 2 > Design.holdtiming

report\_timing -path full -delay max -max\_paths 10 -nworst 2 > Design.setuptiming

report\_area -hierarchy > Design.area

report\_power -hier -hier\_level 2 > Design.power

report\_resources > Design.resources

report\_constraint -verbose > Design.constraint

check\_design > Design.check\_design

check\_timing > Design.check\_timing

- 1. RTL coding

- 2. Technology lib setup

- 3. Constraints

- 4. Major synthesis commands

- 5. Gate-level simulation

# Slight Modification of Original Testbench.v

- RTL simulation: design.v + testbench.v

- Gate-level simulation:

- design.vg

- design.sdf (from DC)

- testbench.v (w/ slight modification)

```

`include "design.v"

`include "design.vg"

`include "stdlib_cells.v"

Module Testbench;

Module Testbench;

....

....

Design u1 (...);

initial $sdf_annotate("design.sdf", u2);

Design u2 (...);

...

•••

endmodule

endmodule

```

- If you meet any questions about some commands

- Use

man set\_input\_delay

- Or

- Search on Baidu/Bing/Google/...

- Synthesis tool makes VLSI design a lot easier

- Easy to use: .v files + .tcl files

- Easy to switch designs to any technology by changing associated libraries

- Easy to have accurate area/timing/power estimate

- Easy to match the best archit. with design constraints

- But... not a substitute for thinking

- Mind your coding styles

- Handmade optimization (e.g. using shift-and-add for variables' multiplication) still needed